# DIGITAL SOUND GENERATOR

- SOUND GENERATED BY READING TABLES CODED IN DELTA CODING OR IN ABSOLUTE VALUES SITUATED IN AN INTERNAL MEMORY OF 16K MAX.

- 16 INDEPENDENT CHANNELS

- 12 BIT EQUIVALENT D/A CONVERTER RESOLUTION (DELTA CODING)

- 8 DIFFERENT TABLE LENGTHS AND 8 READING MODES GIVING A TOTAL OF 58 DISTINCT COMBINATIONS

- 16 DIFFERENT MIXABLE LAYERS BE-TWEEN TWO SEPARATE TABLES

- MULTIPLE READING PERMITS INTERPO-LATION BETWEEN TWO ADJOINING SAMPLES ON THE SAME TABLE

- 4 SELECTABLE ANALOG OUTPUTS

- 10 BIT INTERNAL ATTENUATOR WITH GRADUAL AMPLITUDE VARIATION

- ROM ENABLE OUTPUT TO MINIMISE EXTERNAL MEMORY POWER CONSUMP-TION

- POSSIBILITY OF SYNCHRONOUS AND ASYNCHRONOUS FREQUENCY-TABLE CHANGE AT THE END OF THE READING TABLE

The M114S must be driven by a microprocessor and needs an external memory.

With this device it is possible to synthesize a large range of sound by simply transcribing the most significant periods of the sound to be reproduced into an external memory and programming a suitable reading sequence for these periods with the use of a microprocessor.

The M114S is realized on a single monolithic silicon chip using low threshold N-channel silicon gate MOS technology and is assembled in plastic DIP.40.

# ABSOLUTE MAXIMUM RATINGS

| Symbol           | Parameter                       | Value                   | Unit |

|------------------|---------------------------------|-------------------------|------|

| $V_{DD}$         | Supply voltage                  | -0.3 to 7               | V    |

| Vı               | Input voltage                   | -0.3 to V <sub>DD</sub> | V    |

| Vo               | Output voltage                  | -0.3 to V <sub>DD</sub> | V    |

| P <sub>tot</sub> | Total package power dissipation | 800                     | mW   |

| T <sub>stg</sub> | Storage temperature             | -65 to 150              | °c   |

| T <sub>op</sub>  | Operating temperature           | 0 to 70                 | °c   |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

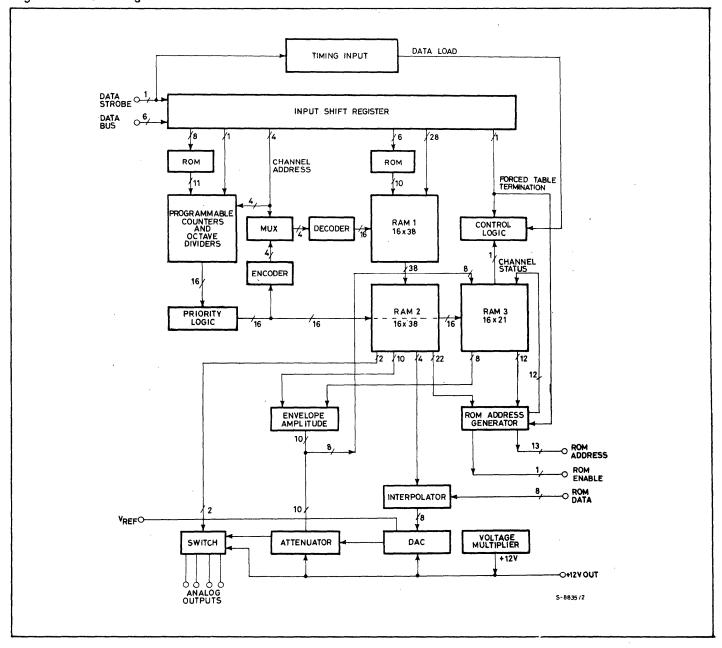

Fig. 1 - Block Diagram

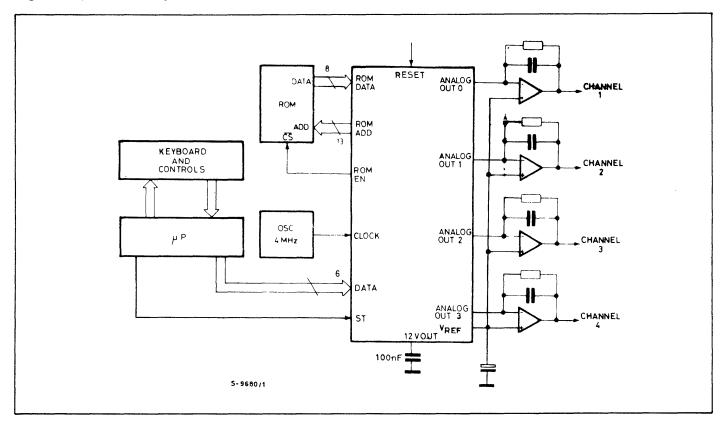

Fig. 2 - System Configuration

# STATIC ELECTRICAL CHARACTERISTICS ( $V_{DD}=5V\pm5\%$ , $V_{SS}=0$ , $T_{amb}=0/70^{\circ}C$ , $V_{DD}$ DIG = $V_{DD}$ Analog)

| Symbol | Parameter  | Test Conditions |      | Value |      | Unit |  |

|--------|------------|-----------------|------|-------|------|------|--|

| Symbol | i arameter | rest Conditions | Min. | Тур.  | Max. | Oint |  |

# INPUTS: RESET (pin 17), CLOCK (pin 16), ROM DATA (pins 26-33), DATA BUS (pins 34-39), DATA ST. (pin 40)

| VIL             | Low Input Level       |                                                     |     | 8.0 | <b>V</b> |

|-----------------|-----------------------|-----------------------------------------------------|-----|-----|----------|

| V <sub>IH</sub> | High Input Level      |                                                     | 2.2 |     | ٧        |

| 1,              | Input Leakage Current | V <sub>I</sub> = V <sub>DD</sub> to V <sub>SS</sub> |     | ± 1 | μΑ       |

# DIGITAL OUTPUTS (HIGH IMPEDANCE\* with 10K $\Omega$ pull-up): ROM-ADD (pins 2-14; 11-17) ROM-EN (pin 25)

| VOL             | Low Output Level  | I <sub>OL</sub> = 1mA   |     | 0.4 | V |

|-----------------|-------------------|-------------------------|-----|-----|---|

| V <sub>OH</sub> | High Output Level | I <sub>OH</sub> = 100μA | 2.4 |     | V |

# **ANALOG OUTPUTS:** (pins 21, 22, 23, 24), V<sub>REF</sub> (pin 19)

| V <sub>REF</sub> | Voltage Reference Output | I <sub>O</sub> = ± 1mA    | 2.5 | V  |

|------------------|--------------------------|---------------------------|-----|----|

| lo               | Output Current           | Zero attenuation          | ± 1 | mΑ |

|                  | (current generator)      | Max input code to the DAC |     |    |

#### **POWER DISSIPATION**

| <u> </u> | 0              |                         | 1 | 100 | ^  |  |  |  |  |

|----------|----------------|-------------------------|---|-----|----|--|--|--|--|

| DD       | Supply Current | V <sub>DD</sub> = 5.25V |   | 120 | mA |  |  |  |  |

<sup>\*</sup> High impedance means that, when the addresses are off, the digital output is connected with an internal resistive pull-up.

#### DYNAMIC ELECTRICAL CHARACTERISTICS

| Symbol                          | Parameter                                 | Test Conditions | Min. | Тур.  | Max. | Unit |

|---------------------------------|-------------------------------------------|-----------------|------|-------|------|------|

| CLOCK                           |                                           |                 |      |       | •    |      |

| tcK                             | Input Clock Frequency                     |                 |      | 4.000 |      | KHz  |

| t <sub>r</sub> , t <sub>f</sub> | Rise and Fall Time                        | 10% to 90%      |      |       | 20   | ns   |

| twH, twL                        | High and Low Pulse Width                  |                 | 80   |       |      | ns   |

| RESET                           |                                           | ,               |      |       |      |      |

| tw                              | Pulse Width                               | Clock = 4 MHz   | 10   |       |      | μs   |

| t <sub>f</sub>                  | Fall Time                                 | 10% to 90%      |      |       | 20   | ns   |

| DATA BUS                        |                                           |                 |      |       |      |      |

| t <sub>W</sub>                  | Pulse Width                               |                 | 750  |       |      | ns   |

| t <sub>set-up</sub>             | Set-up Time to DATA Strobe                |                 | 0    |       |      | ns   |

| <sup>t</sup> hold               | Hold time from DATA Strobe                |                 | 750  |       |      | ns   |

| DATA STR                        | OBE                                       |                 |      |       |      |      |

| t <sub>W</sub>                  | Pulse width                               |                 | 1.5  |       | 128  | μs   |

| twR                             | Pulse Width for Internal Reset generation |                 | 128  |       |      | μs   |

| t <sub>f</sub> , t <sub>r</sub> | Pulse and Fall Times                      |                 |      |       | 100  | ns   |

| tLOW                            |                                           |                 |      | 600   |      | ns   |

| tHIGH                           |                                           |                 |      | 350   |      | ns   |

| t <sub>set~up</sub> (*)         | Set-up Time ROM-EN                        |                 | 70   |       |      | ns   |

<sup>(\*)</sup> t<sub>set-up</sub> time means that the data coming from ext. ROM must be stable at least 70 nsec before the rising edge of ROM-EN.

### PIN FUNCTIONS

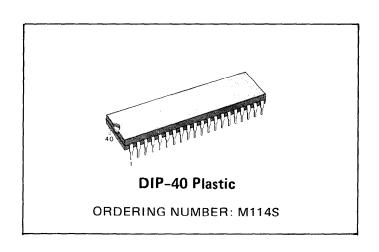

PIN 1 — GND (Analog and Digital)

Analog ground and digital ground are both linked to this pin.

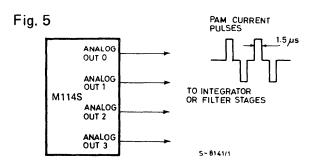

#### Pins 21-24 — Analog Outputs

These outputs are under current with an output impedance of approximately 1  $K\Omega$  and the filter or external integrator must have a low input impedance. This means that the voltage drop between output pin and  $V_{REF}$  must be negligeable so as to obtain a good signal linearity.

An integrator together with a low pass filter are necessary if the tables have been "DELTA" coded. If on the other hand they have been coded in absolute values then only a low pass filter is needed.

If the channels do not have to be separated for stereophonic effects or otherwise, a single output may be used routing, by  $\mu P$  programming, all channels to this pin.

# Pin 19 — Voltage Reference Output ( $V_{REF}$ ) $V_{REF}$ is the average value of the DAC output.

$V_{REF}$  is the average value of the DAC output. With  $V_{supply} = 5V V_{REF}$  is nominally 2.5V but could vary by chip to chip ( $\sim 10 \text{mV}$ ).

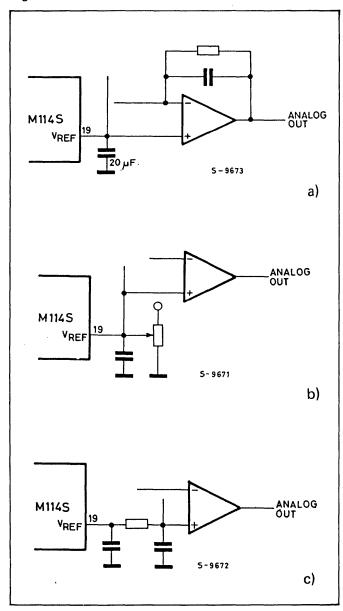

It's only necessary to filter the  $V_{REF}$  output with an external capacitor of some tens of  $\mu F$  (Fig. 3a). To get a voltage suitable to act as  $V_{REF}$  towards external integrator which reconstruct the output signal. Since such a voltage is quite the same than DAC output for a null input code, it automatically conforms itself, following possible differencies between various device instances. It is possible to modify slightly, from the external environment, the obtained  $V_{REF}$  value with suitable resistive networks so that the operational integrator offset can be compensated. (Fig. 3b) To improve the  $V_{REF}$  it's possible to use a filter as in Fig. 3c.

## PIN FUNCTIONS (continued)

Fig. 3.

### Pin 18 — Analog Power Supply

The power supply for all analog parts, i.e. DAC, attenuator, etc...., are linked to this pin.

It is therefore important that this power supply should be very stable and well smoothed.

The internal power supply chip separation allows a great improvement of signal/noise ratio.

#### Pin 15 — Digital Power Supply

The power supply for all digital parts, i.e. counters, memories, etc...., are linked to this pin.

#### Pin 17 - RESET

All channels are reset by raising this pin and the 13 external ROM address outputs together with the 4 sound outputs are placed in a high impedance state.

#### Pin 16 - CLOCK (4 MHz)

For correct functioning the generator must be external to the chip and the duty cycle must be very close to 50%.

The internal programmable counters switch on the positive leading edge.

#### Pin 20 (+12V out)

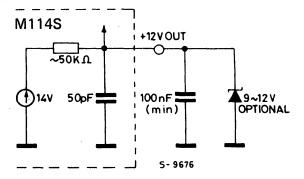

This pin is the output of an internal voltage elevator and it needs of an external filtering capacitance (min. 100 nF).

The performance of DAC and attenuator are very improved with an external zener that clamps the voltage elevator output (see Fig. 4).

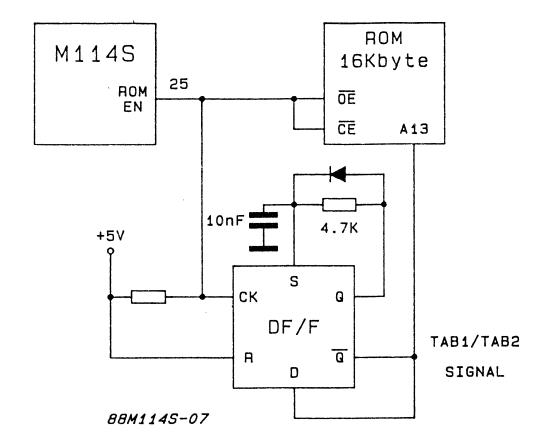

### Pins 25 — ROM-ENABLE (Low active)

This is a PUSH-PULL type output and is used to set the external memory in stand-by so as to reduce consumption whenever it is not read. It is possible to double the addressable memory size (16 Kbyte by connecting this pin to the MSB address line of the external memory trough an F/F.

#### Pins 26 & 33 - ROM-DATA

8 input pins for data from external memory.

#### Pins 2 & 14 - ROM-ADDRESS

13 PUSH-PULL type output pins for external memory address.

#### Pins 34-39 — DATA-BUS

6 input pins for data from the microprocessor. 8 of these data groups make up a complete piece of information.

### Pin 40 - DATA-BUS Strobe

A signal from the microprocessor must arrive at this input in order to memorise the present code onto the DATA-BUS.

Memorization occurs on both edges.

Fig. 4

### GENERAL DESCRIPTION

The M114S is a device that allows digital sound synthesis.

The essential system needed consists of a microprocessor, an M114S and an external memory with a maximum of 8192 bytes.

Sound generation is based on cyclic reading of a table corresponding to a waveform of the timbre to be reproduced.

As the waveform and therefore also the spectrum frequently change, a series of tables of form and frequency appropriate to the sound are cyclically scanned during sound reproduction.

The effect caused by the sudden passage from one table to the next would be unpleasant unless there is such a large number of tables to allow a smooth unnoticeable change from one table to the following.

A favourable compromise between number of tables and quality of sound, that has been implemented in the M114S is the following: A limited number of tables which may even diverge from one another are chosen during an initial phase of analysis after which, during the reproduction phase, two adjoining tables are read simultaneously by extracting a percentage of one and the remaining percentage of the other.

Therefore by starting with 100% of one and zero of the other and successively increasing the second while decreasing the first, so that the sum of the percentages is always equal to 100, there will come a point at which there is a 100% of the second and zero of the first thus having achieved a smooth passage from one table to the next. In the M114S this passage is made up of a maximum of 16 steps.

The tables are stored in an external memory and may be of eight different lengths ranging from 16 to 2048 bytes. The M114S can handle up to a maximum of 16Kbytes (see fig. 8).

The tables may be coded using waveform's absolute value or by the difference between adjoining samples, that is, in a incremental manner (Delta coding).

The typical resolution in Delta coding is 12 bit with a sinusoidal wave coded in a 16-byte table.

A low pass filter at the output is sufficient in the first case to reconstruct the original signal, but very long tables would be necessary for low frequency sounds causing a waste of memory. With the use of an integrator at the output in the second case, the waveforms are coded thus allowing easy interpolation. By simply reading the same data n time and dividing the amplitude of each reading by n, a ramp of n small steps is obtained instead of a large single step.

The value of n may be 1, 2 or 4.

When a waveform is coded in this way (Delta-Coding or incrementally), one must check that the sum of the samples in an entire period is always equal to zero or there would be a continuity which could even saturate the external integrator.

Always the M114S completes the reading of a table before the starting of another. This too avoids saturation of the external integrator. Whenever it is necessary to suddenly move from one table to another before the read cycle has been completed the FTT forced table termination code must be forwarded to the 8 frequency bits.

It is possible to drive the M114S in such a way that the programmed frequency becomes active immediately, without waiting for the running table to end (asynchronous mode); or that this change of frequency occurs only at the end of the running table (synchrounous-mode).

## ASYNCHRONOUS MODE (SET UP AT RESET)

The frequency-information in a command causes the immediate change of the frequency, while the table and all the other parameters are changed only when the running table has been completely scanned.

This type of operation is useful for producing vibrato effects on long tables or vibrato effects on low frequency sounds.

In fact in these cases it is useful to be able to vary continuously the scanning frequency of the same table, without being bound to execute the variation of frequency at the end of the table.

#### SYNCHRONOUS MODE

The frequency-information in a command causes the synchronous change of table and frequency; this is obtained by delaying the frequency change until the running table has been completely scanned.

## GENERAL DESCRIPTION (continued)

This command is very useful in some special effects (glide) because it avoids the reading of the table in part with the old frequency and in part with the new one, thus causing an audible click.

This way-to-operate is useful in the reproduction of deep vibrato on notes placed at the octave boundary, for glide effects and in any case when it is necessary to go beyond the octave boundary without discontinuity.

In fact in these causes it is necessary to schedule in the M114S a length of table and a table frequency scanning completely different from the previous programming.

To avoid clicks it is indispensable to finish the old table with the old frequency before starting the new one with new frequency.

The feature is obtained by acting in global synchronous mode.

The commands for synchronization are:

- **SSG** Set Global Sync. (FB Hex Code). Activates the global synchronous mode i.e. sinchronize, also the frequency change with the table end.

- RSG Reset Sync. Global (F9 Hex Code). This command disables global synchronous mode.

- RSS Reverse Sync. Status (FA Hex Code). This command inverts the synchronism state only for the next programming sequence.

Everyone of these three commands is accomplished by sending a complete programming sequence with F9/FA/FB frequency codes, respectively.

They affect the whole working mode of the device (all its channels).

All the remaining bits are ignored.

Note that the RSS command can be obtained by sending eight times the 6-bit data 111110.

As shown in Tab. 3, there are six bit among the control bits that are dedicated to the choice of table pair length and n number of repeated readings of each table.

The frequency of sample readings is synchronous.

This means that the frequency is a whole multiple of the table length.

In this way any problem caused by intermodula tion is eliminated but a noise due to "collision" is produced. As there is a single output circuit for all channels, that is interpolator, D/A converter, attenuator, ecc., each time more than one channel requires access to this circuit one or more other channels must wait.

The amount of time necessary for the output circuit to process each table, that is the period of time for which each channel uses the circuit during each sample reading cycle, is of  $2\mu s$ . The delay will therefore be proportional to the number of channels operating simultaneously and to the frequency that they are generating. As these parameters casually vary, so will the delay thus producing a casual alteration of the original waveform.

Simulation has proved that under worst possible conditions the signal/noise ratio due to this problem is around 60dB.

In conclusion let us mention the envelope that has to be controlled by the microprocessor which, at suitable intervals, must forward the desired attenuation coefficient.

There are 64 possible attenuations each with steps of approximately 0.75dB;

These passage from one level to another may be immediate or to gradual increments of 1/256 of the maximum amplitude at a frequency proportional to external table reading frequency.

#### **OPERATION**

The M114S receives from the  $\mu P$  a single programming sequence at a time. This programming sequence is made up of 48 bits.

The  $\mu P$  must send a 48 bit set for every M114S active channel.

Each M114S channel continuously generates the same signal, that is it reads the same table, with the same mixing coefficient, with the same amplitude, ecc., until the microprocessor forwards a different programming sequence (variation of one or more parameters characterising the sound to be generated within a single channel.

Timbre amplitude evolution and any other slight frequency changes must be handled in real-time by the microprocessor.

Often the microprocessor is unable to update the amplitude with sufficient speed. For this reason the M114S carries out a gradual change from one amplitude to another at steps of 1/256 of maximum sample frequency amplitude if the change in level is greater than 128 steps, of 1/2 of this frequency if greater than 64, of 1/4 if greater than 32 and of 1/8 if smaller than or equal to 32 steps.

Each channel reads two samples at the sample frequency by taking one from each table, sums them according to the mixing coefficient and forwards the result to the DAC whose suitably attenuated output goes to the previously selected output pin (Fig. 5).

## GENERAL DESCRIPTION (continued)

This operation requires  $2\mu s$  and as there is a single output circuit for all channels it is certain that one or more channels will simultaneously request the use of the circuit. Thus a priority order has been assigned to each channel. This order is fixed, channel zero being that of greatest priority followed in order by the others.

When more than one channel is simultaneously active at the output pin there will be an overlap of impulse sequence of each channel.

The example of Fig. 6 shows an output signal with 2 active channels, CH1 has greater priority

The signal will change from impulsive to continuous by passing through:

- a low pass filter if the table have been coded using absolute values.

- an integrator if in delta coding

#### **PROGRAMMING**

48 bits subdivided into 8 groups of 6 bits each must be forwarded in order to programme a channel.

A group of 6 bits is memorised on every Data Strobe switch front. As the data bus is read approximately 250ns after transition from the Data Strobe, the 6 data bits may simultaneously arrive with the Delta Strobe switch.

#### DATA PROGRAMMING ORDER

| N. PIN<br>BYTE  | 34                | 35           | 36                                 | 37             | 38      | 39      |  |  |

|-----------------|-------------------|--------------|------------------------------------|----------------|---------|---------|--|--|

| 1st             |                   |              | ATTEN                              | JATION         |         |         |  |  |

|                 | A5                | A4           | A3                                 | A2             | A1      | A0      |  |  |

| 2 <sup>nd</sup> | 4 OU <sup>.</sup> | TPUTS        | TABLE 1                            | ADDRESS        | TABLE 2 | ADDRESS |  |  |

| 22              | 1                 | 0            | 7                                  | 6              | 7       | 6       |  |  |

| 3 <sup>rd</sup> |                   |              | TABLE 2                            | ADDRESS        |         |         |  |  |

| 3               | 5 .               | 4            | 3                                  | 2              | . 1     | 0       |  |  |

| 4th             | TABLE 1 ADDRESS   |              |                                    |                |         |         |  |  |

| 4               | 5                 | 4            | 3                                  | 2              | 1       | 0       |  |  |

| 5 <sup>th</sup> |                   | TABLE LENGTI | Н                                  | READING METHOD |         |         |  |  |

| 5***            | L2                | L1           | LO                                 | M2             | M1      | MO      |  |  |

| 6 <sup>th</sup> |                   | INTERPO      | RPOLATION IMMEDIATE CONNECTION DIV |                |         |         |  |  |

| ρ               | 3                 | 2            | 1                                  | 0              | 0       | 0       |  |  |

| 7 <sup>th</sup> |                   | CHANNE       | L NUMBER                           |                | FREQU   | JENCY   |  |  |

| ,               | 3                 | 2            | 1                                  | 0              | 1       | 0       |  |  |

| gth             |                   |              | FREQU                              | JENCY          |         |         |  |  |

|                 | 7                 | 6            | 5                                  | 4              | 3       | 2       |  |  |

## GENERAL DESCRIPTION (continued)

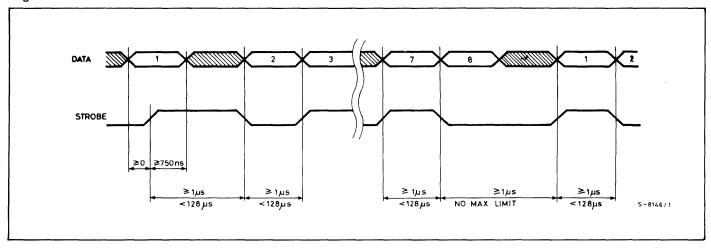

The graph of fig. 7shows the time lapse that must be assigned to these signal for correct functioning.

No more than  $128\mu s$  must pass between one Data Strobe transition and the next during transmission of the 8 groups of data or else synchronisation is lost due to the internal automatic reset generated after 128µs from the last Data Strobe transition, causing the data to be misinterpreted.

One should wait for at least 9µs after the forcedzero-cross command has been given between the last group of data of one instruction and the first group of the next.

Fig. 7

The degree of priority of the channel and the number of channels in use at that moment must be taken into account in order to shorten this wait, If there is maximum priority the wait will be a minimum wait of approximately  $2\mu$ s. The same holds if the priority is not maximum but there are no other channels in use. There will however be a maximum wait of  $2\mu$ s for each active channel with greater priority than the channel in question.

If another instruction were to be transmitted without a sufficient wait, there would be the risk of losing the previous instruction of forced table. termination.

The wait is unnecessary after normal commands.

Every data group must be remain present for at least 1µs after Data Strobe transition.

The 48 bit functions are the following:

- A) 8 address bits for the 1<sup>st</sup> table (ext. ROM)

B) 8 address bits for the 2<sup>nd</sup> table (ext ROM)

C) 8 frequency bits (4-note and 4-twelfths of note and ± 1 or 2/1000)

- D) 6 attenuation or amplitude address bits

- E) 4 interpolation bits

- F) 4 channel address bits

- 6 reading mode and table length bits (ext. G) ROM)

- 2 bits for choice between four outputs H)

- 1 bit for a frequency octave change

- 1 bit for gradual disable of envelope

While waiting for the present 1st table reading to terminate, the above data (not immediately operational) is memorized into the internal RAM 1).

The new data is transfered to RAM2 and becomes operational when the addressed channel ends the current table scanning.

An exception is made by the 8 frequency bits and the one varying the frequency octave as they operate immediately (See synchronization).

All data may be made operational by giving the forced-table-termination command.

### 48 PROGRAMMING BIT FOR CHANNEL **SELECTION**

### 8 Address Bits 1st Table (ext. ROM)

These determine the most significant part of the 13 external memory address bits but according to the table length chosen by the 6 mode bits, some of the least significant of these 8 bits are suitably substituted by the M114S.

In the case of a maximum table length, 2048 bytes, there will only be 2 significant bits to address the table while the remaining 11 will address each single table word.

By already knowing the table length, the programmer will be able to programme the most significant bits needed for table address only and ignore the others.

As the maximum memory that can be handled is of 8Kbytes, if the table has a length of 1Kbyte it is sufficient to program the 3 MSB bits and ignore the other five.

# 48 PROGRAMMING BIT FOR CHANNEL SELECTION (continued)

# 8 Address Bits 2<sup>nd</sup> Table (ext. ROM))

As above but refering to the second table.

One must consider that the forced table termination refers to the first table and that during table mixing the second table may assume a percentage value of zero while the first table can only assume a minimum percentage value of 1/16 of the maximum value.

8 Frequency Bits

The 4 most significant bits characterize one of the 15 available notes with HEX. Codes from 0 to E. Eleven movements in twelfths of a semitone may be obtained with the remaining 4 bits as well as four  $\pm$  1/1000 and  $\pm$  2/1000 note frequency variations.

These permit the production of: Vibrato, Glissando, chorus effect etc....

The FF codes correspond to the forced-table-termination command while FC maintains the previous frequency. F9, FA, FB are synchronisation commands. The F8 code = ROMID is a ROM identification command.

It just sets the programmable counters of the M114S to a very short counting modulo (8 + 0) useless for musical purposes.

The remaining codes are used for testing and therefore must not be used by the operator. Table 1 shows the 240 frequencies obtainable by setting the external clock to 4MHz and the table length to 16 bytes, with single reading and without inserting an octave divisor. These are the highest octave frequencies obtainable with the M114S.

In practice double, quadruple, etc . . . frequencies may be obtained by writing 2, 4, etc. complete waveform periods in the table.

#### 6 Attenuation Bits

These are the addresses for the internal attenuation table.

The contents of this table follow a logarithmic pattern so as to produce a decrease of 0.75dB for each address unit increment. See table 2. The word length is of 10 bits.

After processing by a suitable circuit in order to obtain a gradual amplitude variation the ten outputs of this table are linked to the 10 bit attenuator.

The gradual movement from the present level to that just programmed takes place by increasing or decreasing the 8 most significant bits of the attenuation table contents, with the same frequency with which the external memory tables are being scanned if the difference in level is greater than 128 steps, or with 1/2 of this frequency if greater than 64 steps or 1/4 if greater than 32, or 1/8 if smaller than or equal to 32.

In conclusion, the output signal amplitude increases of decreases at each variation by 1/256 of the maximum value.

By setting the bit that deals with the gradual envelope there is an immediate passage from

the present level to that programmed.

#### 4 Interpolation Bits

These define the mixing coefficient between the two waveform tables.

It is possible in this way to sum the 1<sup>st</sup> waveform percentage with the remaining 2<sup>nd</sup> waveform percentage thus obtaining a third signal which will be forward to the output.

In greater detail, the operation carried out is the following:

$$D = (D1 * (K + 1)/16) + (D2 * (15 - K)/16)$$

#### where

- D is the data at the input of the DAC (8 bits in complement with 2)

- D1 is the data read from the 1<sup>st</sup> table (8 bits in complement with 2)

- D2 is the data read from the 2<sup>nd</sup> table (8 bits in complement with 2)

- K is a 4 bit interpolation coefficient (from 0 to 15)

Obviously only the first waveform will be output if K = 15.

#### 4 Channel Address Bits

These indicate to which of the 16 M114S channel the remaining 44 bits will be forwarded.

#### 6 Mode Bits

These indicate the table couple reading mode (ext. ROM).

For each table there are 58 distinct combinations that include, both table lengths and the number of repeated readings from the same address. (ext ROM). See table n. 3.

The three most significant bits characterize the table lengths while the other three characterise the length ratio between tables and the number of repeated readings.

#### 2 Output Address Bits

These indicate to which of the 4 output pins the corresponding channel signal must be forwarded. This is necessary in order to obtain stereophonic effect or to separate channels used for accompanyment from those of "SOLO", etc. . .

#### 1 Octave Divisor Bit

This is used to pass from one octave to another without changing the table length. If octave divisor bit is set to 1 the programming frequency is divided by two.

## 1 Instant ENVELOPE Change Bit

This orders instant passage from the present amplitude to that programmed.

TABLE 1 - FREQUENCIES

| NOTE | DEVIATION | -6/12              | -5/12              | -4/12              | -3/12              | -2/12              | -1/12              | -2/1000            | -1/1000            |

|------|-----------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

|      | (Hex)     | 0                  | 1                  | 2                  | 3                  | 4                  | 5                  | 6                  | 7                  |

| С    | 0         | 1016.78            | 1021.45            | 1026.69            | 1031.46            | 1036.27            | 1041.67            | 1044.39            | 1045.48            |

| C#   | 1<br>2    | 1077.01<br>1140.90 | 1082.25<br>1146.79 | 1087.55<br>1152.07 | 1092.90<br>1158.08 | 1098.30<br>1163.47 | 1103.14<br>1168.91 | 1106.81<br>1172.33 | 1107.42            |

| D#   | 3         | 1209.19            | 1215.07            | 1221.00            | 1226.99            | 1232.29            | 1238.39            | 1242.24            | 1173.71<br>1243.78 |

| E    | 4         | 1281.23            | 1287.00            | 1293.66            | 1299.55            | 1305.48            | 1312.34            | 1315.79            | 1317.52            |

| F    | 5         | 1356.85            | 1363.33            | 1369.86            | 1376.46            | 1383.13            | 1389.85            | 1393.73            | 1395.67            |

| F#   | 6         | 1437.81            | 1445.09            | 1451.38            | 1458.79            | 1466.28            | 1472.75            | 1478.20            | 1479.29            |

| G    | 7         | 1523.23            | 1530.22            | 1538.46            | 1545.60            | 1552.80            | 1560.06            | 1564.95            | 1566.17            |

| G#   | 8         | 1614.21            | 1622.06            | 1629.99            | 1638.00            | 1644.74            | 1652.89            | 1658.37            | 1659.75            |

| Α    | 9         | 1709.40            | 1718.21            | 1727.12            | 1734.61            | 1743.68            | 1751.31            | 1757.47            | 1759.01            |

| A#   | Α         | 1811.59            | 1819.84            | 1829.83            | 1838.24            | 1846.72            | 1855.29            | 1860.47            | 1862.20            |

| В    | В         | 1919.39            | 1928.64            | 1937.98            | 1947.42            | 1956.95            | 1966.57            | 1972.39            | 1974.33            |

| 2C   | С         | 2032.52            | 2042.90            | 2053.39            | 2063.98            | 2072.54            | 2083.33            | 2087.68            | 2089.86            |

| 2C#  | D         | 2155.17            | 2164.50            | 2176.28            | 2185.79            | 2195.39            | 2207.51            | 2212.39            | 2214.84            |

| 2D   | E         | 2283.11            | 2293.58            | 2304.15            | 2314.81            | 2325.58            | 2339.18            | 2344.67            | 2347.42            |

|      | F         | For                |

|      |           | Testing            |

| NOTE                    | DEVIATION                                                | 0                                                                                                                                | +1/1000                                                                                                                          | +2/1000                                                                                                                          | +1/12                                                                                                                 | +2/12                                                                                                                            | +3/12                                                                                                                            | +4/12                                                                                                                            | +5/12                                                                                                                            |

|-------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

|                         | (Hex)                                                    | 8                                                                                                                                | 9                                                                                                                                | Α                                                                                                                                | В                                                                                                                     | С                                                                                                                                | D                                                                                                                                | Е                                                                                                                                | F                                                                                                                                |

| C # D # E F # G # A # B | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>A<br>B | 1046.57<br>1108.65<br>1174.40<br>1244.56<br>1318.39<br>1396.65<br>1480.38<br>1567.40<br>1661.13<br>1760.56<br>1863.93<br>1976.28 | 1047.67<br>1109.88<br>1175.78<br>1245.33<br>1319.26<br>1397.62<br>1481.48<br>1568.63<br>1662.51<br>1762.11<br>1865.67<br>1978.24 | 1048.77<br>1111.11<br>1177.16<br>1246.88<br>1321.00<br>1398.60<br>1482.58<br>1569.86<br>1663.89<br>1763.89<br>1867.41<br>1980.20 | 1051.52<br>1114.21<br>1180.64<br>1250.78<br>1324.50<br>1403.51<br>1486.99<br>1576.04<br>1669.45<br>1768.35<br>1874.41 | 1056.52<br>1119.19<br>1186.24<br>1256.28<br>1331.56<br>1410.44<br>1494.77<br>1583.53<br>1677.85<br>1777.78<br>1883.24<br>1994.02 | 1061.57<br>1124.86<br>1191.90<br>1262.63<br>1337.79<br>1417.43<br>1501.50<br>1591.09<br>1684.92<br>1785.71<br>1892.15<br>2004.01 | 1066.67<br>1130.58<br>1197.60<br>1269.04<br>1344.09<br>1424.50<br>1508.30<br>1598.72<br>1693.48<br>1793.72<br>1901.14<br>2014.10 | 1071.81<br>1135.72<br>1203.37<br>1274.70<br>1350.44<br>1430.62<br>1516.30<br>1606.43<br>1702.13<br>1803.43<br>1910.22<br>2024.29 |

| 2C<br>2C#<br>2D         | C<br>D<br>E<br>F                                         | 2092.05<br>2217.29<br>2350.18<br>ROMID                                                                                           | 2094.24<br>2219.76<br>2352.94<br>SSG                                                                                             | 2096.44<br>2222.22<br>2355.71<br>RSS                                                                                             | 2103.05<br>2227.17<br>2361.28<br>RSG                                                                                  | 2114.16<br>2239.64<br>2372.48<br>Previously<br>Selected<br>Frequency                                                             | 2123.14<br>2249.72<br>2383.79<br>For<br>Testing                                                                                  | 2134,47<br>2259,89<br>2395,21<br>For<br>Testing                                                                                  | 2143.62<br>2272.73<br>2406.74<br>Forced<br>Table<br>Terminat.                                                                    |

# **TABLE 2** — ATTENUATION

N = six bit attenuation code decimal value (0 : 63)

V = internally decoded linear ten bit value (0 : 1023)

A = theoretical attenuation value in decibels =  $20 \cdot \text{Log} ((V + 1)/1024)$

|          | ·           |       |

|----------|-------------|-------|

| N        | V           | Α     |

| 0        | 1023        | 0.00  |

| 1        | 939         | 0.74  |

| 2        | 863         | 1.48  |

| 3        | 791         | 2.23  |

| 4        | 727         | 2.96  |

| 5        | 667         | 3.71  |

| 6        | 611         | 4.47  |

| 7        | 559         | 5.24  |

| 8        | 515         | 5.95  |

| 9        | 471         | 6.73  |

| 10       | 431         | 7.50  |

| 11       | 395         | 8.25  |

| 12       | 363         | 8.98  |

| 13       | 335         | 9.68  |

| 14       | 307         | 10.43 |

| 15       | <b>28</b> 3 | 11.14 |

| 16       | 259         | 11.91 |

| 17       | 235         | 12.75 |

| 18       | 215         | 13.52 |

| 19       | 199         | 14.19 |

| 20       | 183         | 14.91 |

| 21       | 166         | 15.75 |

| 22       | 152         | 16.51 |

| 23       | 140         | 17.22 |

| 24       | 128         | 17.99 |

| 25       | 117         | 18.77 |

| 26       | 107         | 19.54 |

| 27       | 98          | 20.29 |

| 28       | 90          | 21.03 |

| 29       | 83          | 21.72 |

| 30       | · 76        | 22.48 |

| 31       | 69          | 23.30 |

| <u> </u> |             |       |

| N  | >          | Α     |        |

|----|------------|-------|--------|

| 32 | 64         | 23.95 |        |

| 33 | 58         | 24.79 |        |

| 34 | <b>5</b> 3 | 25.56 |        |

| 35 | 49         | 26.23 |        |

| 36 | 45         | 26.95 |        |

| 37 | 41         | 27.74 |        |

| 38 | 37         | 28.61 |        |

| 39 | 34         | 29.32 |        |

| 40 | 31         | 30.10 |        |

| 41 | 28         | 30.96 | İ      |

| 42 | 26         | 31.58 |        |

| 43 | 24         | 32.25 |        |

| 44 | 22         | 32.97 |        |

| 45 | 20         | 33.76 |        |

| 46 | 18         | 34.63 |        |

| 47 | 16         | 35.60 |        |

| 48 | 14         | 36.68 |        |

| 49 | 13         | 37.28 |        |

| 50 | 12         | 37.93 |        |

| 51 | 11         | 38.62 |        |

| 52 | 10         | 39.38 | •      |

| 53 | 9          | 40.21 |        |

| 54 | 8          | 41.12 |        |

| 55 | 7          | 42.14 |        |

| 56 | 6          | 43.30 |        |

| 57 | 5          | 44.64 |        |

| 58 | 4          | 46.23 | ,      |

| 59 | 3          | 48.16 |        |

| 60 | 2          | 50.66 |        |

| 61 | 1          | 54.19 |        |

| 62 | 0          | 60.21 |        |

| 63 | 0          | 60.21 | + STOP |

| 1  |            | l     |        |

**TABLE 3 - READING MODES**

| MODE |     | LENGTH |      | READ N. |    |

|------|-----|--------|------|---------|----|

| М    | L   | T1     | T2   | Т1      | Т2 |

| 000  | 000 | 16     | 16   | 2       | 2  |

| 000  | 001 | 32     | 32   | 2       | 2  |

| 000  | 010 | 64     | 64   | 2       | 2  |

| 000  | 011 | 128    | 128  | 2       | 2  |

| 000  | 100 | 256    | 256  | 2       | 2  |

| 000  | 101 | 512    | 512  | 2       | 2  |

| 000  | 110 | 1024   | 1024 | 2       | 2  |

| 000  | 111 | 2048   | 1048 | 2       | 2  |

| 001  | 000 | 16     | 16   | 1       | 1  |

| 001  | 001 | 32     | 32   | 1       | 1  |

| 001  | 010 | 64     | 64   | 1       | 1  |

| 001  | 011 | 128    | 128  | 1       | 1  |

| 001  | 100 | 256    | 256  | 1       | 1  |

| 001  | 101 | 512    | 512  | 1       | 1  |

| 001  | 110 | 1024   | 1024 | 1       | 1  |

| 001  | 111 | 2048   | 2048 | 1       | 1  |

| 010  | 000 | 16     | 16   | 4       | 4  |

| 010  | 001 | 32     | 32   | 4       | 4  |

| 010  | 010 | 64     | 64   | 4       | 4  |

| 010  | 011 | 128    | 128  | 4       | 4  |

| 010  | 100 | 256    | 256  | 4       | 4  |

| 010  | 101 | 512    | 512  | 4       | 4  |

| 010  | 110 | 1024   | 1024 | 4       | 4  |

| 010  | 111 | 1024*  | 1024 | 4       | 4  |

| 011  | 000 | 16     | 16\$ | 1       | 1  |

| 011  | 001 | 32     | 16   | 1       | 1  |

| 011  | 010 | 64     | 32   | 1       | 1  |

| 011  | 011 | 128    | 64   | 1       | 1  |

| 011  | 100 | 256    | 128  | 1       | 1  |

| 011  | 101 | 512    | 256  | 1       | 1  |

| 011  | 110 | 1024   | 512  | 1       | 1  |

| 011. | 111 | 2048   | 1024 | 1       | 1  |

| MODE |     | LENGTH |      | READ N. |    |

|------|-----|--------|------|---------|----|

| М    | L   | Т1     | T2   | T1      | Т2 |

| 100  | 000 | 16     | 8    | 1       | 2  |

| 100  | 001 | 32     | 16   | 1       | 2  |

| 100  | 010 | 64     | 32   | 1       | 2  |

| 100  | 011 | 128    | 64   | 1       | 2  |

| 100  | 100 | 256    | 128  | 1       | 2  |

| 100  | 101 | 512    | 256  | 1       | 2  |

| 100  | 110 | 1024   | 512  | 1       | 2  |

| 100  | 111 | 2048   | 1024 | 1       | 2  |

| 101  | 000 | 16     | 16\$ | 1       | 1  |

| 101  | 001 | 32     | 16\$ | 1       | 1  |

| 101  | 010 | 64     | 16   | 1       | 1  |

| 101  | 011 | 128    | 32   | 1       | 1  |

| 101  | 100 | 256    | 64   | 1       | 1  |

| 101  | 101 | 512    | 128  | 1       | 1  |

| 101  | 110 | 1024   | 256  | 1       | 1  |

| 101  | 111 | 2048   | 512  | 1       | 1  |

| 110  | 000 | 16     | 4    | 1       | 4  |

| 110  | 001 | 32     | 8    | 1       | 4  |

| 110  | 010 | 64     | 16   | 1       | 4  |

| 110  | 011 | 128    | 32   | 1       | 4  |

| 110  | 100 | 256    | 64   | 1       | 4  |

| 110  | 101 | 512    | 128  | 1       | 4  |

| 110  | 110 | 1024   | 256  | 1       | 4  |

| 110  | 111 | 2048   | 512  | 1       | 4  |

| 111  | 000 | 16     | 16\$ | 1       | 1  |

| 111  | 001 | 32     | 16\$ | 1       | 1  |

| 111  | 010 | 64     | 16\$ | 1       | 1  |

| 111  | 011 | 128    | 16   | 1       | 1  |

| 111  | 100 | 256    | 32   | 1       | 1  |

| 111  | 101 | 512    | 64   | 1       | 1  |

| 111  | 110 | 1024   | 128  | 1       | 1  |

| 111  | 111 | 2048   | 256  | 1       | 1  |

<sup>\*</sup> Repetitions

<sup>\$</sup> Exceptions

Fig. 8 - The M114S can handle up to 16Kbyte of memory with this application circuit.